Single-chip 16-bit/32-bit microcontrollers; 512 kB flash, with 32 segment x 4 LCD driver

Rev. 01 — 15 October 2008

**Product data sheet**

## 1. General description

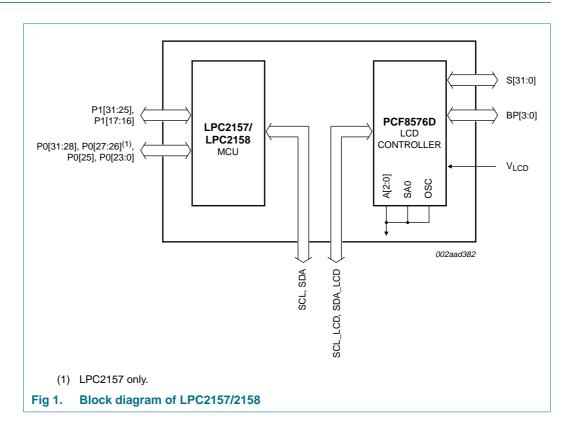

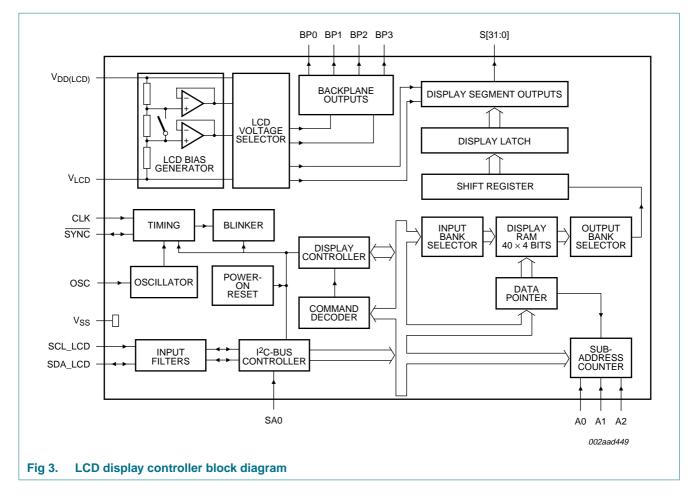

The LPC2157/2158 is a multi-chip module consisting of a LPC2138/2148 single-chip microcontroller combined with a PCF8576D Universal LCD driver in a low-cost 100-pin package. The LCD driver provides 32 segments and supports from 1 to 4 backplanes. Display overhead is minimized by an on-chip display RAM with auto-increment addressing. Refer to the respective LPC2148 and LPC2138 user manual for details.

## 2. Features

128-bit wide interface/accelerator enables high-speed 60 MHz operation.

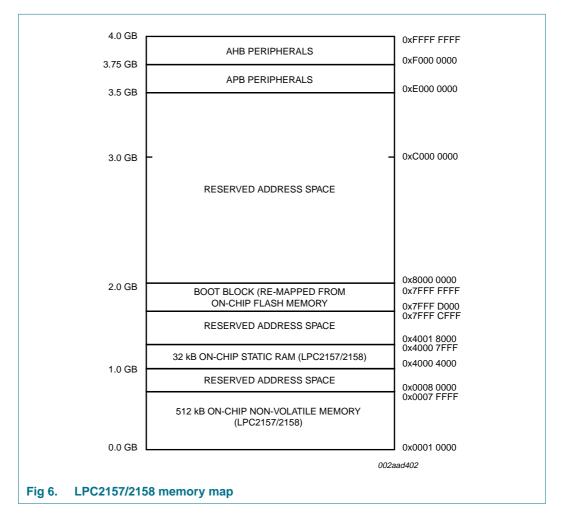

32 kB to 40 kB of on-chip static RAM and 512 kB of on-chip flash memory.

- USB 2.0 Full-speed compliant device controller with 2 kB of endpoint RAM.

An additional 8 kB of on-chip RAM accessible to USB by DMA (LPC2158 only).

- 32 segment × 4 backplane LCD controller supports from 1 to 4 backplanes.

- Single 10-bit DAC provides variable analog output.

- Low power Real-Time Clock (RTC) with independent power and 32 kHz clock input.

- Multiple serial interfaces including two UARTs (16C550), two Fast I<sup>2</sup>C-bus (400 kbit/s), SPI and SSP with buffering and variable data length capabilities.

- High-accuracy internal RC oscillator option allows operation without external oscillator components. The RC oscillator option is selectable and fine tunable.

- 2.4 V to 3.6 V V<sub>DD</sub> operating range. I/O pins are 5 V tolerant (may be pulled up or driven to 5.5 V).

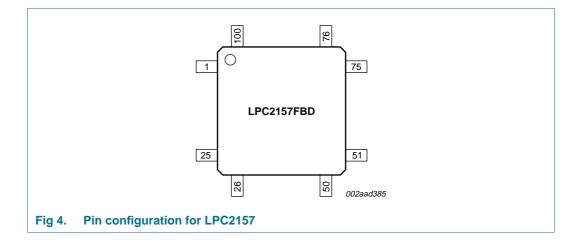

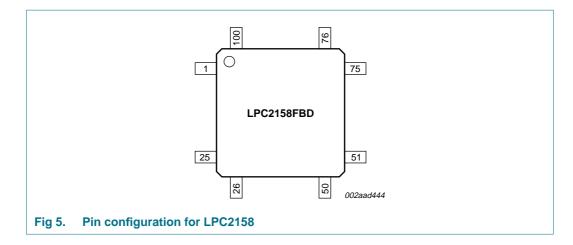

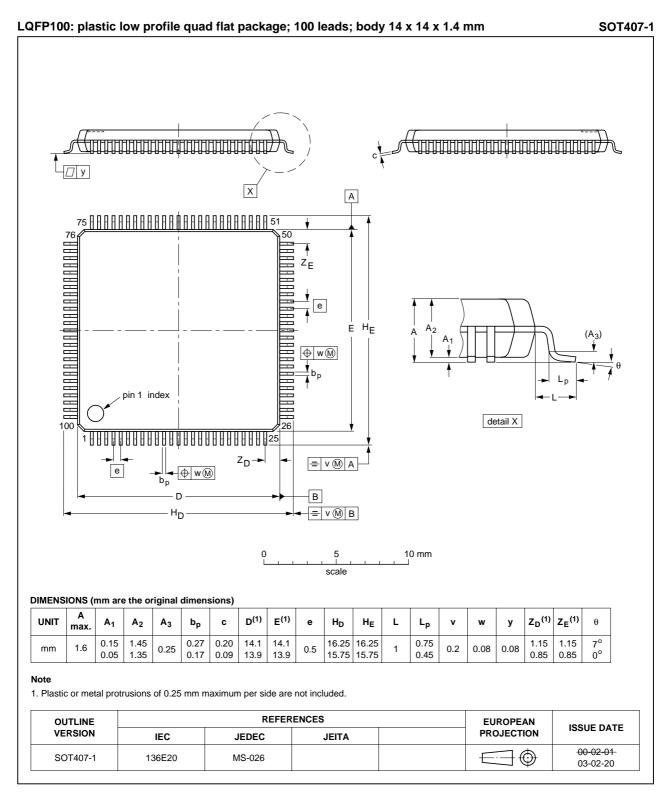

- 100-pin LQFP package with 38 microcontroller I/O pins minimum.

- Individual enable/disable of peripheral functions as well as peripheral clock scaling for additional power optimization.

## 3. Ordering information

#### Table 1.Ordering information

| Type number   | Package | Package                                                                               |          |  |  |  |

|---------------|---------|---------------------------------------------------------------------------------------|----------|--|--|--|

|               | Name    | Description                                                                           | Version  |  |  |  |

| LPC2157FBD100 | LQFP100 | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm   | SOT407-1 |  |  |  |

| LPC2158FBD100 | LQFP100 | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm | SOT407-1 |  |  |  |

Single-chip 16-bit/32-bit microcontrollers

## 4. Block diagram

## LPC2157/2158

#### Single-chip 16-bit/32-bit microcontrollers

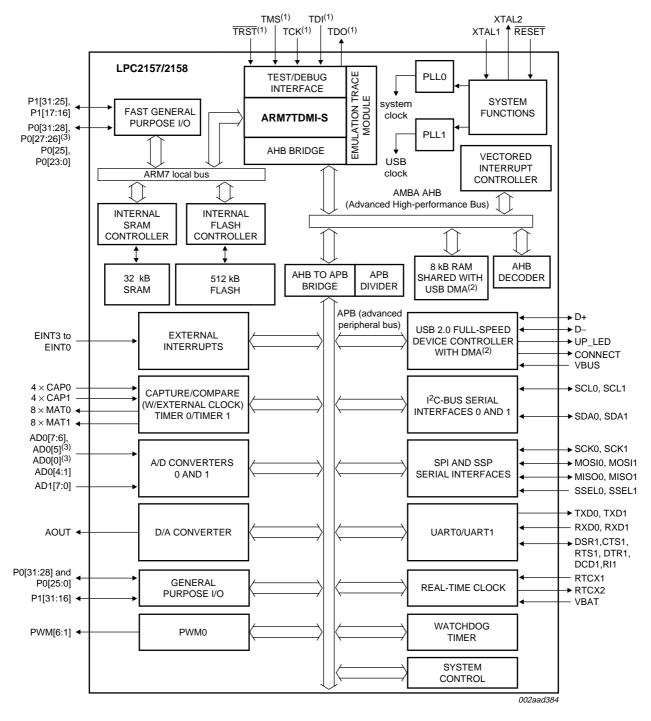

(1) Pins shared with GPIO.

(2) USB DMA controller with 8 kB of RAM accessible as general purpose RAM and/or DMA is available in LPC2158 only.

(3) LPC2157 only.

#### Fig 2. Microcontroller section block diagram

### Single-chip 16-bit/32-bit microcontrollers

## 5. Pinning information

5.1 Pinning

### Single-chip 16-bit/32-bit microcontrollers

## 5.2 Pin description

| Table 2. Pin des | scription LF        | PC2157 |                                                                                                                                                                                                                                                                                                                        |  |

|------------------|---------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Pin                 | Туре   | Description                                                                                                                                                                                                                                                                                                            |  |

| P0[0] to P0[31]  |                     | I/O    | <b>Port 0:</b> Port 0 is a 32-bit I/O port with individual direction controls for each bit. Total of 31 pins of the Port 0 can be used as a general purpose bidirectional digital I/Os while P0[31] is output only pin. The operation of port 0 pins depends upon the pin function selected via the pin connect block. |  |

|                  |                     |        | Pin P0[24] is not available.                                                                                                                                                                                                                                                                                           |  |

| P0[0]/TXD0/      | 7 <u>[1]</u>        | I/O    | P0[0] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |  |

| PWM1             |                     | 0      | <b>TXD0</b> — Transmitter output for UART0.                                                                                                                                                                                                                                                                            |  |

|                  |                     | 0      | <b>PWM1</b> — Pulse Width Modulator output 1.                                                                                                                                                                                                                                                                          |  |

| P0[1]/RXD0/      | 9 <mark>[2]</mark>  | I/O    | P0[1] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |  |

| PWM3/EINT0       |                     | I      | <b>RXD0</b> — Receiver input for UART0.                                                                                                                                                                                                                                                                                |  |

|                  |                     | 0      | PWM3 — Pulse Width Modulator output 3.                                                                                                                                                                                                                                                                                 |  |

|                  |                     | I      | EINT0 — External interrupt 0 input.                                                                                                                                                                                                                                                                                    |  |

| P0[2]/SCL0/      | 10 <mark>[3]</mark> | I/O    | P0[2] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |  |

| CAP0[0]          |                     | I/O    | SCL0 — I <sup>2</sup> C0 clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                                                                                  |  |

|                  |                     | I      | CAP0[0] — Capture input for Timer 0, channel 0.                                                                                                                                                                                                                                                                        |  |

| P0[3]/SDA0/      | 14 <mark>[3]</mark> | I/O    | P0[3] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |  |

| MAT0[0]/EINT1    |                     | I/O    | <b>SDA0</b> — I <sup>2</sup> C0 data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                                                                            |  |

|                  |                     | 0      | MAT0[0] — Match output for Timer 0, channel 0.                                                                                                                                                                                                                                                                         |  |

|                  |                     | I      | EINT1 — External interrupt 1 input.                                                                                                                                                                                                                                                                                    |  |

| P0[4]/SCK0/      | 15 <mark>[4]</mark> | I/O    | P0[4] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |  |

| CAP0[1]/AD0[6]   |                     | I/O    | SCK0 — Serial clock for SPI0. SPI clock output from master or input to slave.                                                                                                                                                                                                                                          |  |

|                  |                     | I      | CAP0[1] — Capture input for Timer 0, channel 1.                                                                                                                                                                                                                                                                        |  |

|                  |                     | I      | AD0[6] — ADC 0, input 6.                                                                                                                                                                                                                                                                                               |  |

| P0[5]/MISO0/     | 17 <mark>[4]</mark> | I/O    | P0[5] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |  |

| MAT0[1]/AD0[7]   |                     | I/O    | <b>MISO0</b> — Master In Slave Out for SPI0. Data input to SPI master or data output from SPI slave.                                                                                                                                                                                                                   |  |

|                  |                     | 0      | MAT0[1] — Match output for Timer 0, channel 1.                                                                                                                                                                                                                                                                         |  |

|                  |                     | I      | AD0[7] — ADC 0, input 7.                                                                                                                                                                                                                                                                                               |  |

# LPC2157/2158

## Single-chip 16-bit/32-bit microcontrollers

| Table 2.Pin des | cription LPC        | <b>C2157</b> co | ontinued                                                                                             |  |                                                                                                                                            |

|-----------------|---------------------|-----------------|------------------------------------------------------------------------------------------------------|--|--------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | Pin                 | Туре            | Description                                                                                          |  |                                                                                                                                            |

| P0[6]/MOSI0/    | 18 <mark>[4]</mark> | I/O             | <b>P0[6]</b> — General purpose input/output digital pin (GPIO).                                      |  |                                                                                                                                            |

| CAP0[2]/AD1[0]  |                     | I/O             | <b>MOSI0</b> — Master Out Slave In for SPI0. Data output from SPI master or data input to SPI slave. |  |                                                                                                                                            |

|                 |                     | I               | CAP0[2] — Capture input for Timer 0, channel 2.                                                      |  |                                                                                                                                            |

|                 |                     | I               | AD1[0] — ADC 1, input 0.                                                                             |  |                                                                                                                                            |

| P0[7]/SSEL0/    | 19 <mark>[2]</mark> | I/O             | P0[7] — General purpose input/output digital pin (GPIO).                                             |  |                                                                                                                                            |

| PWM2/EINT2      |                     | I               | SSEL0 — Slave Select for SPI0. Selects the SPI interface as a slave.                                 |  |                                                                                                                                            |

|                 |                     | 0               | <b>PWM2</b> — Pulse Width Modulator output 2.                                                        |  |                                                                                                                                            |

|                 |                     | I               | EINT2 — External interrupt 2 input.                                                                  |  |                                                                                                                                            |

| P0[8]/TXD1/     | 20[4]               | I/O             | P0[8] — General purpose input/output digital pin (GPIO).                                             |  |                                                                                                                                            |

| PWM4/AD1[1]     |                     | 0               | <b>TXD1</b> — Transmitter output for UART1.                                                          |  |                                                                                                                                            |

|                 |                     | 0               | <b>PWM4</b> — Pulse Width Modulator output 4.                                                        |  |                                                                                                                                            |

|                 |                     | I               | AD1[1] — ADC 1, input 1.                                                                             |  |                                                                                                                                            |

| P0[9]/RXD1/     | 21 <mark>2</mark>   | I/O             | P0[9] — General purpose input/output digital pin (GPIO).                                             |  |                                                                                                                                            |

| PWM6/EINT3      |                     | I               | <b>RXD1</b> — Receiver input for UART1.                                                              |  |                                                                                                                                            |

|                 |                     | 0               | <b>PWM6</b> — Pulse Width Modulator output 6.                                                        |  |                                                                                                                                            |

|                 |                     | I               | EINT3 — External interrupt 3 input.                                                                  |  |                                                                                                                                            |

| P0[10]/RTS1/    | 22 <mark>[4]</mark> | I/O             | P0[10] — General purpose input/output digital pin (GPIO).                                            |  |                                                                                                                                            |

| CAP1[0]/AD1[2]  |                     | 0               | <b>RTS1</b> — Request to Send output for UART1.                                                      |  |                                                                                                                                            |

|                 |                     | I               | <b>CAP1[0]</b> — Capture input for Timer 1, channel 0.                                               |  |                                                                                                                                            |

|                 |                     | Ι               | AD1[2] — ADC 1, input 2.                                                                             |  |                                                                                                                                            |

| P0[11]/CTS1/    | 23 <mark>[3]</mark> | I/O             | <b>P0[11]</b> — General purpose input/output digital pin (GPIO).                                     |  |                                                                                                                                            |

| CAP1[1]/SCL1    |                     | I               | <b>CTS1</b> — Clear to Send input for UART1.                                                         |  |                                                                                                                                            |

|                 |                     | I               | <b>CAP1[1]</b> — Capture input for Timer 1, channel 1.                                               |  |                                                                                                                                            |

|                 |                     | I/O             | SCL1 — $I^2C1$ clock input/output. Open-drain output (for $I^2C$ -bus compliance)                    |  |                                                                                                                                            |

| P0[12]/DSR1/    | 24 <mark>[4]</mark> | I/O             | P0[12] — General purpose input/output digital pin (GPIO).                                            |  |                                                                                                                                            |

| MAT1[0]/AD1[3]  |                     | I               | DSR1 — Data Set Ready input for UART1.                                                               |  |                                                                                                                                            |

|                 |                     | 0               | MAT1[0] — Match output for Timer 1, channel 0.                                                       |  |                                                                                                                                            |

|                 |                     | I               | AD1[3] — ADC 1 input 3.                                                                              |  |                                                                                                                                            |

| P0[13]/DTR1/    | 25 <mark>[4]</mark> | I/O             | P0[13] — General purpose input/output digital pin (GPIO).                                            |  |                                                                                                                                            |

| MAT1[1]/AD1[4]  |                     | 0               | <b>DTR1</b> — Data Terminal Ready output for UART1.                                                  |  |                                                                                                                                            |

|                 |                     | 0               | MAT1[1] — Match output for Timer 1, channel 1.                                                       |  |                                                                                                                                            |

|                 |                     | I               | AD1[4] — ADC 1 input 4.                                                                              |  |                                                                                                                                            |

| P0[14]/DCD1/    | 26 <mark>[3]</mark> | I/O             | P0[14] — General purpose input/output digital pin (GPIO).                                            |  |                                                                                                                                            |

| EINT1/SDA1      |                     | I               | DCD1 — Data Carrier Detect input for UART1.                                                          |  |                                                                                                                                            |

|                 |                     | I               | EINT1 — External interrupt 1 input.                                                                  |  |                                                                                                                                            |

|                 |                     | I/O             | <b>SDA1</b> — $I^2C1$ data input/output. Open-drain output (for $I^2C$ -bus compliance).             |  |                                                                                                                                            |

|                 |                     |                 |                                                                                                      |  | <b>Note:</b> LOW on this pin while $\overrightarrow{RESET}$ is LOW forces on-chip bootloader to take over control of the part after reset. |

Table 2.

Pin description LPC2157 ...continued

# LPC2157/2158

## Single-chip 16-bit/32-bit microcontrollers

| Symbol          | Pin                 | Туре | Description                                                                                         |

|-----------------|---------------------|------|-----------------------------------------------------------------------------------------------------|

| P0[15]/RI1/     | 28 <mark>[4]</mark> | I/O  | P0[15] — General purpose input/output digital pin (GPIO).                                           |

| EINT2/AD1[5]    |                     | Ι    | <b>RI1</b> — Ring Indicator input for UART1.                                                        |

|                 |                     | Ι    | EINT2 — External interrupt 2 input.                                                                 |

|                 |                     | Ι    | AD1[5] — ADC 1, input 5.                                                                            |

| P0[16]/EINT0/   | 29 <mark>[2]</mark> | I/O  | P0[16] — General purpose input/output digital pin (GPIO).                                           |

| MAT0[2]/CAP0[2] |                     | I    | EINT0 — External interrupt 0 input.                                                                 |

|                 |                     | 0    | MAT0[2] — Match output for Timer 0, channel 2.                                                      |

|                 |                     | I    | CAP0[2] — Capture input for Timer 0, channel 2.                                                     |

| P0[17]/CAP1[2]/ | 30 <mark>[1]</mark> | I/O  | P0[17] — General purpose input/output digital pin (GPIO).                                           |

| SCK1/MAT1[2]    |                     | I    | CAP1[2] — Capture input for Timer 1, channel 2.                                                     |

|                 |                     | I/O  | SCK1 — Serial Clock for SSP. Clock output from master or input to slave.                            |

|                 |                     | 0    | MAT1[2] — Match output for Timer 1, channel 2.                                                      |

| P0[18]/CAP1[3]/ | 79 <mark>[1]</mark> | I/O  | P0[18] — General purpose input/output digital pin (GPIO).                                           |

| MISO1/MAT1[3]   |                     | Ι    | CAP1[3] — Capture input for Timer 1, channel 3.                                                     |

|                 |                     | I/O  | <b>MISO1</b> — Master In Slave Out for SSP. Data input to SPI master or data outpu from SSP slave.  |

|                 |                     | 0    | MAT1[3] — Match output for Timer 1, channel 3.                                                      |

| P0[19]/MAT1[2]/ | 80 <mark>[1]</mark> | I/O  | P0[19] — General purpose input/output digital pin (GPIO).                                           |

| MOSI1/CAP1[2]   |                     | 0    | MAT1[2] — Match output for Timer 1, channel 2.                                                      |

|                 |                     | I/O  | <b>MOSI1</b> — Master Out Slave In for SSP. Data output from SSP master or data input to SSP slave. |

|                 |                     | I    | CAP1[2] — Capture input for Timer 1, channel 2.                                                     |

| P0[20]/MAT1[3]/ | 812                 | I/O  | P0[20] — General purpose input/output digital pin (GPIO).                                           |

| SSEL1/EINT3     |                     | 0    | MAT1[3] — Match output for Timer 1, channel 3.                                                      |

|                 |                     | I    | SSEL1 — Slave Select for SSP. Selects the SSP interface as a slave.                                 |

|                 |                     | I    | EINT3 — External interrupt 3 input.                                                                 |

| P0[21]/PWM5/    | 91 <mark>4]</mark>  | I/O  | P0[21] — General purpose input/output digital pin (GPIO).                                           |

| AD1[6]/CAP1[3]  |                     | 0    | <b>PWM5</b> — Pulse Width Modulator output 5.                                                       |

|                 |                     | I    | AD1[6] — ADC 1, input 6.                                                                            |

|                 |                     | I    | CAP1[3] — Capture input for Timer 1, channel 3.                                                     |

| P0[22]/AD1[7]/  | 92 <mark>[4]</mark> | I/O  | P0[22] — General purpose input/output digital pin (GPIO).                                           |

| CAP0[0]/        |                     | Ι    | AD1[7] — ADC 1, input 7.                                                                            |

| MAT0[0]         |                     | Ι    | CAP0[0] — Capture input for Timer 0, channel 0.                                                     |

|                 |                     | 0    | <b>MAT0[0]</b> — Match output for Timer 0, channel 0.                                               |

| P0[23]          | 84 <mark>[1]</mark> | I/O  | P0[23] — General purpose input/output digital pin (GPIO).                                           |

| P0[25]/AD0[4]/  | 97 <mark>5</mark>   | I/O  | P0[25] — General purpose input/output digital pin (GPIO).                                           |

| AOUT            |                     | I    | AD0[4] — ADC 0, input 4.                                                                            |

|                 |                     | 0    | AOUT — DAC output.                                                                                  |

| P0[26]/AD0[5]   | 98 <mark>[7]</mark> | I/O  | P0[26] — General purpose input/output digital pin (GPIO).                                           |

|                 |                     | Ι    | <b>AD0[5]</b> — ADC 0, input 5. This analog input is always connected to its pin.                   |

## LPC2157\_2158\_1

# LPC2157/2158

## Single-chip 16-bit/32-bit microcontrollers

| Symbol          | Pin                 | Туре | Description                                                                                                                                                                                                                                                               |

|-----------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[27]/AD0[0]/  | 99 <mark>[7]</mark> | I/O  | P0[27] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

| CAP0[1]/MAT0[1] |                     | I    | AD0[0] — ADC 0, input 0. This analog input is always connected to its pin.                                                                                                                                                                                                |

|                 |                     | I    | CAP0[1] — Capture input for Timer 0, channel 1.                                                                                                                                                                                                                           |

|                 |                     | 0    | MAT0[1] — Match output for Timer 0, channel 1.                                                                                                                                                                                                                            |

| P0[28]/AD0[1]/  | 1 <u>[4]</u>        | I/O  | P0[28] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

| CAP0[2]/MAT0[2] |                     | I    | AD0[1] — ADC 0, input 1.                                                                                                                                                                                                                                                  |

|                 |                     | Ι    | CAP0[2] — Capture input for Timer 0, channel 2.                                                                                                                                                                                                                           |

|                 |                     | 0    | MAT0[2] — Match output for Timer 0, channel 2.                                                                                                                                                                                                                            |

| P0[29]/AD0[2]/  | 2[4]                | I/O  | P0[29] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

| CAP0[3]/MAT0[3] |                     | I    | AD0[2] — ADC 0, input 2.                                                                                                                                                                                                                                                  |

|                 |                     | Ι    | CAP0[3] — Capture input for Timer 0, channel 3.                                                                                                                                                                                                                           |

|                 |                     | 0    | MAT0[3] — Match output for Timer 0, channel 3.                                                                                                                                                                                                                            |

| P0[30]/AD0[3]/  | 3 <u>[4]</u>        | I/O  | <b>P0[30]</b> — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                          |

| EINT3/CAP0[0]   |                     | I    | AD0[3] — ADC 0, input 3.                                                                                                                                                                                                                                                  |

|                 |                     | Ι    | EINT3 — External interrupt 3 input.                                                                                                                                                                                                                                       |

|                 |                     | I    | CAP0[0] — Capture input for Timer 0, channel 0.                                                                                                                                                                                                                           |

| P0[31]          | 5 <u>[6]</u>        | 0    | P0[31] — General purpose output only digital pin.                                                                                                                                                                                                                         |

| P1[0] to P1[31] |                     | I/O  | <b>Port 1:</b> Port 1 is a 32-bit bidirectional I/O port with individual direction controls for each bit. The operation of port 1 pins depends upon the pin function selected via the pin connect block. Pins 0 through 15 and 18 through 24 of port 1 are not available. |

| P1[16]          | 4 <mark>[6]</mark>  | I/O  | P1[16] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

| P1[17]          | 100 <mark>6</mark>  | I/O  | P1[17] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

| P1[25]/EXTIN0   | 16 <mark>6</mark>   | I/O  | P1[25] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

|                 |                     | I    | EXTIN0 — External Trigger Input. Standard I/O with internal pull-up.                                                                                                                                                                                                      |

| P1[26]/RTCK     | 12 <mark>6]</mark>  | I/O  | P1[26] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

|                 |                     | I/O  | <b>RTCK</b> — Returned Test Clock output. Extra signal added to the JTAG port.<br>Assists debugger synchronization when processor frequency varies.<br>Bidirectional pin with internal pull-up.                                                                           |

|                 |                     |      | <b>Note:</b> LOW on RTCK while RESET is LOW enables pins P1[31:26] to operate as Debug port after reset.                                                                                                                                                                  |

| P1[27]/TDO      | 90 <mark>6</mark>   | I/O  | P1[27] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

|                 |                     | 0    | <b>TDO</b> — Test Data out for JTAG interface.                                                                                                                                                                                                                            |

| P1[28]/TDI      | 86 <mark>6]</mark>  | I/O  | P1[28] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

|                 |                     | I    | <b>TDI</b> — Test Data in for JTAG interface.                                                                                                                                                                                                                             |

| P1[29]/TCK      | 82 <mark>6]</mark>  | I/O  | P1[29] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

|                 |                     | I    | TCK — Test Clock for JTAG interface.                                                                                                                                                                                                                                      |

| P1[30]/TMS      | 78 <mark>6]</mark>  | I/O  | P1[30] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

|                 |                     | I    | TMS — Test Mode Select for JTAG interface.                                                                                                                                                                                                                                |

| P1[31]/TRST     | 8 <mark>[6]</mark>  | I/O  | P1[31] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                 |

|                 |                     | I    | <b>TRST</b> — Test Reset for JTAG interface.                                                                                                                                                                                                                              |

|                 |                     |      |                                                                                                                                                                                                                                                                           |

. .

1 000455

## LPC2157/2158

#### Single-chip 16-bit/32-bit microcontrollers

| Table 2.             | Pin descr | ription LPC                     | 2157coi | ntinued                                                                                                                                                                                                                |

|----------------------|-----------|---------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol               |           | Pin                             | Туре    | Description                                                                                                                                                                                                            |

| RESET                |           | 83 <mark>[8]</mark>             | I       | <b>External reset input:</b> A LOW on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. TTL with hysteresis, 5 V tolerant. |

| XTAL1                |           | 88 <mark>9]</mark>              | 0       | Input from the oscillator amplifier.                                                                                                                                                                                   |

| XTAL2                |           | 87 <mark>9]</mark>              | I       | Output to the oscillator circuit and internal clock generator circuits.                                                                                                                                                |

| RTCX1                |           | 93 <mark>9</mark>               | I       | Input to the RTC oscillator circuit.                                                                                                                                                                                   |

| RTCX2                |           | 94 <mark>9</mark>               | 0       | Output from the RTC oscillator circuit.                                                                                                                                                                                |

| V <sub>SS</sub>      |           | 6, 13, 32,<br>39, 40,<br>85, 95 | I       | Ground: 0 V reference.                                                                                                                                                                                                 |

| $V_{DD}$             |           | 11, 27, 33                      | I       | <b>3.3 V power supply:</b> This is the power supply voltage for the core and I/O ports.                                                                                                                                |

| V <sub>DDA</sub>     |           | 96                              | I       | <b>Analog 3.3 V power supply:</b> This should be nominally the same voltage as $V_{DD}$ but should be isolated to minimize noise and error. This voltage is only used to power the on-chip ADC(s) and DAC.             |

| V <sub>DD(LCD)</sub> |           | 38                              | I       | 1.8 V to 5.5 V power supply: Power supply voltage for the PCF8576D.                                                                                                                                                    |

| $V_{LCD}$            |           | 41                              | I       | LCD power supply: LCD voltage.                                                                                                                                                                                         |

| VREF                 |           | 89                              | I       | <b>ADC reference voltage:</b> This should be nominally less than or equal to the $V_{DD}$ voltage but should be isolated to minimize noise and error. Level on this pin is used as a reference for ADC(s) and DAC.     |

| VBAT                 |           | 31                              | I       | <b>RTC power supply voltage:</b> 3.3 V on this pin supplies the power to the RTC.                                                                                                                                      |

| SDA_LCD              | )         | 34                              | I/O     | <b>SDA LCD</b> — I <sup>2</sup> C-bus data signal for the LCD controller.                                                                                                                                              |

| SCL_LCD              | )         | 35                              | I       | SCL LCD — I <sup>2</sup> C-bus clock signal for the LCD controller.                                                                                                                                                    |

| SYNC                 |           | 36                              | I/O     | <b>SYNC</b> — cascade synchronization input/output                                                                                                                                                                     |

| CLK                  |           | 37                              | I/O     | CLK — external clock input/output                                                                                                                                                                                      |

| BP0 to BF            | 23        | 42 to 45                        | 0       | BP0 to BP3: LCD backplane outputs.                                                                                                                                                                                     |

| S0 to S31            |           | 46 to 77                        | 0       | S0 to S31: LCD segment outputs.                                                                                                                                                                                        |

[1] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis and 10 ns slew rate control.

[2] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis and 10 ns slew rate control. If configured for an input function, this pad utilizes built-in glitch filter that blocks pulses shorter than 3 ns.

[3] Open-drain 5 V tolerant digital I/O I<sup>2</sup>C-bus 400 kHz specification compatible pad. It requires external pull-up to provide an output functionality.

[4] 5 V tolerant pad providing digital I/O (with TTL levels and hysteresis and 10 ns slew rate control) and analog input function. If configured for an input function, this pad utilizes built-in glitch filter that blocks pulses shorter than 3 ns. When configured as an ADC input, digital section of the pad is disabled.

[5] 5 V tolerant pad providing digital I/O (with TTL levels and hysteresis and 10 ns slew rate control) and analog output function. When configured as the DAC output, digital section of the pad is disabled.

[6] 5 V tolerant pad with built-in pull-up resistor providing digital I/O functions with TTL levels and hysteresis and 10 ns slew rate control. The pull-up resistor's value typically ranges from 60 k $\Omega$  to 300 k $\Omega$ .

[7] Pad is designed in accordance with the Universal Serial Bus (USB) specification, revision 2.0 (Full-speed and Low-speed mode only).

[8] 5 V tolerant pad providing digital input (with TTL levels and hysteresis) function only.

[9] Pad provides special analog functionality.

# LPC2157/2158

## Single-chip 16-bit/32-bit microcontrollers

| Table 3. | Pin | description LPC2158 | \$  |

|----------|-----|---------------------|-----|

|          |     |                     | · . |

| Symbol          | Pin                 | Туре | Description                                                                                                                                                                                                                                                                                                            |

|-----------------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[0] to P0[31] |                     | I/O  | <b>Port 0:</b> Port 0 is a 32-bit I/O port with individual direction controls for each bit. Total of 29 pins of the Port 0 can be used as a general purpose bidirectional digital I/Os while P0[31] is output only pin. The operation of port 0 pins depends upon the pin function selected via the pin connect block. |

|                 |                     |      | Pins P0[24], P0[26] and P0[27] are not available.                                                                                                                                                                                                                                                                      |

| P0[0]/TXD0/     | 7 <u>[1]</u>        | I/O  | P0[0] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |

| PWM1            |                     | 0    | <b>TXD0</b> — Transmitter output for UART0.                                                                                                                                                                                                                                                                            |

|                 |                     | 0    | <b>PWM1</b> — Pulse Width Modulator output 1.                                                                                                                                                                                                                                                                          |

| P0[1]/RXD0/     | 9 <mark>[2]</mark>  | I/O  | <b>P0[1]</b> — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                        |

| PWM3/EINT0      |                     | I    | <b>RXD0</b> — Receiver input for UART0.                                                                                                                                                                                                                                                                                |

|                 |                     | 0    | <b>PWM3</b> — Pulse Width Modulator output 3.                                                                                                                                                                                                                                                                          |

|                 |                     | I    | EINT0 — External interrupt 0 input.                                                                                                                                                                                                                                                                                    |

| P0[2]/SCL0/     | 10 <mark>3]</mark>  | I/O  | <b>P0[2]</b> — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                        |

| CAP0[0]         |                     | I/O  | <b>SCL0</b> — $I^2C0$ clock input/output. Open-drain output (for $I^2C$ -bus compliance).                                                                                                                                                                                                                              |

|                 |                     | I    | <b>CAP0[0]</b> — Capture input for Timer 0, channel 0.                                                                                                                                                                                                                                                                 |

| P0[3]/SDA0/     | 14 <mark>3]</mark>  | I/O  | <b>P0[3]</b> — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                        |

| MAT0[0]/EINT1   |                     | I/O  | <b>SDA0</b> — I <sup>2</sup> C0 data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                                                                            |

|                 |                     | 0    | <b>MAT0[0]</b> — Match output for Timer 0, channel 0.                                                                                                                                                                                                                                                                  |

|                 |                     | I    | EINT1 — External interrupt 1 input.                                                                                                                                                                                                                                                                                    |

| P0[4]/SCK0/     | 15 <mark>[4]</mark> | I/O  | <b>P0[4]</b> — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                        |

| CAP0[1]/AD0[6]  |                     | I/O  | SCK0 — Serial clock for SPI0. SPI clock output from master or input to slave.                                                                                                                                                                                                                                          |

|                 |                     | I    | CAP0[1] — Capture input for Timer 0, channel 1.                                                                                                                                                                                                                                                                        |

|                 |                     | I    | AD0[6] — ADC 0, input 6.                                                                                                                                                                                                                                                                                               |

| P0[5]/MISO0/    | 17 <mark>4]</mark>  | I/O  | <b>P0[5]</b> — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                        |

| MAT0[1]/AD0[7]  |                     | I/O  | <b>MISO0</b> — Master In Slave Out for SPI0. Data input to SPI master or data output from SPI slave.                                                                                                                                                                                                                   |

|                 |                     | 0    | MAT0[1] — Match output for Timer 0, channel 1.                                                                                                                                                                                                                                                                         |

|                 |                     | I    | AD0[7] — ADC 0, input 7.                                                                                                                                                                                                                                                                                               |

| P0[6]/MOSI0/    | 18 <mark>[4]</mark> | I/O  | P0[6] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |

| CAP0[2]/AD1[0]  |                     | I/O  | <b>MOSI0</b> — Master Out Slave In for SPI0. Data output from SPI master or data input to SPI slave.                                                                                                                                                                                                                   |

|                 |                     | I    | CAP0[2] — Capture input for Timer 0, channel 2.                                                                                                                                                                                                                                                                        |

|                 |                     | I    | AD1[0] — ADC 1, input 0.                                                                                                                                                                                                                                                                                               |

| P0[7]/SSEL0/    | 19 <mark>[2]</mark> | I/O  | P0[7] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |

| PWM2/EINT2      |                     | I    | SSEL0 — Slave Select for SPI0. Selects the SPI interface as a slave.                                                                                                                                                                                                                                                   |

|                 |                     | 0    | <b>PWM2</b> — Pulse Width Modulator output 2.                                                                                                                                                                                                                                                                          |

|                 |                     | I    | EINT2 — External interrupt 2 input.                                                                                                                                                                                                                                                                                    |

| P0[8]/TXD1/     | 20 <mark>[4]</mark> | I/O  | P0[8] — General purpose input/output digital pin (GPIO).                                                                                                                                                                                                                                                               |

| PWM4/AD1[1]     |                     | 0    | TXD1 — Transmitter output for UART1.                                                                                                                                                                                                                                                                                   |

|                 |                     | 0    | <b>PWM4</b> — Pulse Width Modulator output 4.                                                                                                                                                                                                                                                                          |

|                 |                     | I    | AD1[1] — ADC 1, input 1.                                                                                                                                                                                                                                                                                               |

# LPC2157/2158

## Single-chip 16-bit/32-bit microcontrollers

| Symbol          | Pin                 | Туре | Description                                                                                                     |

|-----------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------|

| P0[9]/RXD1/     | 21 <mark>2</mark>   | I/O  | P0[9] — General purpose input/output digital pin (GPIO).                                                        |

| PWM6/EINT3      |                     | I    | <b>RXD1</b> — Receiver input for UART1.                                                                         |

|                 |                     | 0    | <b>PWM6</b> — Pulse Width Modulator output 6.                                                                   |

|                 |                     | I    | EINT3 — External interrupt 3 input.                                                                             |

| P0[10]/RTS1/    | 22 <mark>[4]</mark> | I/O  | <b>P0[10]</b> — General purpose input/output digital pin (GPIO).                                                |

| CAP1[0]/AD1[2]  |                     | 0    | RTS1 — Request to Send output for UART1.                                                                        |

|                 |                     | I    | CAP1[0] — Capture input for Timer 1, channel 0.                                                                 |

|                 |                     | I    | AD1[2] — ADC 1, input 2.                                                                                        |

| P0[11]/CTS1/    | 23 <mark>3</mark>   | I/O  | P0[11] — General purpose input/output digital pin (GPIO).                                                       |

| CAP1[1]/SCL1    |                     | I    | <b>CTS1</b> — Clear to Send input for UART1.                                                                    |

|                 |                     | I    | CAP1[1] — Capture input for Timer 1, channel 1.                                                                 |

|                 |                     | I/O  | SCL1 — I <sup>2</sup> C1 clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance)            |

| P0[12]/DSR1/    | 24 <mark>[4]</mark> | I/O  | P0[12] — General purpose input/output digital pin (GPIO).                                                       |

| MAT1[0]/AD1[3]  |                     | I    | DSR1 — Data Set Ready input for UART1.                                                                          |

|                 |                     | 0    | MAT1[0] — Match output for Timer 1, channel 0.                                                                  |

|                 |                     | I    | AD1[3] — ADC 1 input 3.                                                                                         |

| P0[13]/DTR1/    | 25 <mark>[4]</mark> | I/O  | P0[13] — General purpose input/output digital pin (GPIO).                                                       |

| MAT1[1]/AD1[4]  |                     | 0    | <b>DTR1</b> — Data Terminal Ready output for UART1.                                                             |

|                 |                     | 0    | MAT1[1] — Match output for Timer 1, channel 1.                                                                  |

|                 |                     | I    | AD1[4] — ADC 1 input 4.                                                                                         |

| P0[14]/DCD1/    | 26 <mark>[3]</mark> | I/O  | P0[14] — General purpose input/output digital pin (GPIO).                                                       |

| EINT1/SDA1      |                     | I    | DCD1 — Data Carrier Detect input for UART1.                                                                     |

|                 |                     | I    | EINT1 — External interrupt 1 input.                                                                             |

|                 |                     | I/O  | SDA1 — I <sup>2</sup> C1 data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).            |

|                 |                     |      | Note: LOW on this pin while RESET is LOW forces on-chip bootloader to tak over control of the part after reset. |

| P0[15]/RI1/     | 28 <mark>[4]</mark> | I/O  | P0[15] — General purpose input/output digital pin (GPIO).                                                       |

| EINT2/AD1[5]    |                     | I    | <b>RI1</b> — Ring Indicator input for UART1.                                                                    |

|                 |                     | I    | EINT2 — External interrupt 2 input.                                                                             |

|                 |                     | I    | AD1[5] — ADC 1, input 5.                                                                                        |

| P0[16]/EINT0/   | 29 <mark>[2]</mark> | I/O  | P0[16] — General purpose input/output digital pin (GPIO).                                                       |

| MAT0[2]/CAP0[2] |                     | I    | EINT0 — External interrupt 0 input.                                                                             |

|                 |                     | 0    | MAT0[2] — Match output for Timer 0, channel 2.                                                                  |

|                 |                     | I    | CAP0[2] — Capture input for Timer 0, channel 2.                                                                 |

| P0[17]/CAP1[2]/ | 30 <mark>[1]</mark> | I/O  | P0[17] — General purpose input/output digital pin (GPIO).                                                       |

| SCK1/MAT1[2]    |                     | I    | CAP1[2] — Capture input for Timer 1, channel 2.                                                                 |

|                 |                     | I/O  | SCK1 — Serial Clock for SSP. Clock output from master or input to slave.                                        |

|                 |                     | 0    | MAT1[2] — Match output for Timer 1, channel 2.                                                                  |

# LPC2157/2158

## Single-chip 16-bit/32-bit microcontrollers

| Symbol                          | Pin                 | Туре | Description                                                                                         |

|---------------------------------|---------------------|------|-----------------------------------------------------------------------------------------------------|

| P0[18]/CAP1[3]/                 | 79 <mark>[1]</mark> | I/O  | P0[18] — General purpose input/output digital pin (GPIO).                                           |

| MISO1/MAT1[3]                   |                     | I    | CAP1[3] — Capture input for Timer 1, channel 3.                                                     |

|                                 |                     | I/O  | <b>MISO1</b> — Master In Slave Out for SSP. Data input to SPI master or data outpu from SSP slave.  |

|                                 |                     | 0    | MAT1[3] — Match output for Timer 1, channel 3.                                                      |

| P0[19]/MAT1[2]/                 | 80 <mark>[1]</mark> | I/O  | P0[19] — General purpose input/output digital pin (GPIO).                                           |

| MOSI1/CAP1[2]                   |                     | 0    | MAT1[2] — Match output for Timer 1, channel 2.                                                      |

|                                 |                     | I/O  | <b>MOSI1</b> — Master Out Slave In for SSP. Data output from SSP master or data input to SSP slave. |

|                                 |                     | I    | CAP1[2] — Capture input for Timer 1, channel 2.                                                     |

| P0[20]/MAT1[3]/                 | 81 <mark>2</mark>   | I/O  | P0[20] — General purpose input/output digital pin (GPIO).                                           |

| SSEL1/EINT3                     |                     | 0    | MAT1[3] — Match output for Timer 1, channel 3.                                                      |

|                                 |                     | I    | SSEL1 — Slave Select for SSP. Selects the SSP interface as a slave.                                 |

|                                 |                     | I    | EINT3 — External interrupt 3 input.                                                                 |

| P0[21]/PWM5/                    | 91 <mark>4]</mark>  | I/O  | P0[21] — General purpose input/output digital pin (GPIO).                                           |

| AD1[6]/CAP1[3]                  |                     | 0    | <b>PWM5</b> — Pulse Width Modulator output 5.                                                       |

|                                 |                     | I    | AD1[6] — ADC 1, input 6.                                                                            |

|                                 |                     | I    | CAP1[3] — Capture input for Timer 1, channel 3.                                                     |

| P0[22]/AD1[7]/                  | 92 <mark>[4]</mark> | I/O  | P0[22] — General purpose input/output digital pin (GPIO).                                           |

| CAP0[0]/<br>MAT0[0]             |                     | Ι    | AD1[7] — ADC 1, input 7.                                                                            |

|                                 |                     | Ι    | CAP0[0] — Capture input for Timer 0, channel 0.                                                     |

|                                 |                     | 0    | MAT0[0] — Match output for Timer 0, channel 0.                                                      |

| P0[23]/V <sub>BUS</sub>         | 84 <u>[1]</u>       | I/O  | P0[23] — General purpose input/output digital pin (GPIO).                                           |

|                                 |                     | Ι    | V <sub>BUS</sub> — Indicates the presence of USB bus power.                                         |

|                                 |                     |      | Note: This signal must be HIGH for USB reset to occur.                                              |

| P0[25]/AD0[4]/                  | 97 <mark>5</mark>   | I/O  | <b>P0[25]</b> — General purpose input/output digital pin (GPIO).                                    |

| AOUT                            |                     | Ι    | AD0[4] — ADC 0, input 4.                                                                            |

|                                 |                     | 0    | AOUT — DAC output.                                                                                  |

| P0[28]/AD0[1]/                  | 1 <u>[4]</u>        | I/O  | <b>P0[28]</b> — General purpose input/output digital pin (GPIO).                                    |

| CAP0[2]/MAT0[2]                 |                     | I    | AD0[1] — ADC 0, input 1.                                                                            |

|                                 |                     | I    | CAP0[2] — Capture input for Timer 0, channel 2.                                                     |

|                                 |                     | 0    | <b>MAT0[2]</b> — Match output for Timer 0, channel 2.                                               |

| P0[29]/AD0[2]/                  | 2 <mark>[4]</mark>  | I/O  | <b>P0[29]</b> — General purpose input/output digital pin (GPIO).                                    |

| CAP0[3]/MAT0[3]                 |                     | I    | AD0[2] — ADC 0, input 2.                                                                            |

|                                 |                     |      | CAP0[3] — Capture input for Timer 0, channel 3.                                                     |

|                                 | - 7 43              | 0    | MAT0[3] — Match output for Timer 0, channel 3.                                                      |

| P0[30]/AD0[3]/<br>EINT3/CAP0[0] | 3 <mark>[4]</mark>  | I/O  | <b>P0[30]</b> — General purpose input/output digital pin (GPIO).                                    |